(11)Publication number : 08-008355(43)Date of publication of application : 12.01.1996

| (51)Int.Cl.                                      |                         | <br>H01L 23/12                    |                                                      |

|--------------------------------------------------|-------------------------|-----------------------------------|------------------------------------------------------|

| (21)Application number :<br>(22)Date of filing : | 06-138770<br>21.06.1994 | (71)Applicant :<br>(72)Inventor : | FUJITSU LTD<br>YAMANISHI GAKUO<br>TSUJIMURA TAKEHISA |

#### (54) SEMICONDUCTOR DEVICE

#### (57)Abstract:

PURPOSE: To enhance electric characteristics and reliability of a semiconductor

device having a large number of outer connection terminals.

CONSTITUTION: The semiconductor device having a plurality of outer connection terminals comprises a semiconductor chip 12 mounted on a substrate 11, a terminal 13 to be connected electrically with a power supply pad among electrode pads 12a formed on the semiconductor chip 12, a terminal 14 to be connected electrically with a ground bad, and signal leads 15 to be connected electrically with signal pads. The power supply connection terminal 13 and the ground connection terminal 14 are arranged on the side of the substrate 11 different from that arranged with the signal lead 15.

### EGAL STATUS

[Date of request for examination]

[Date of sending the examiner's decision of rejection]

Kind of final disposal of application other than the examiner's decision of rejection or application converted registration]

[Date of final disposal for application]

[Patent number]

[Date of registration]

Number of appeal against examiner's decision of rejection] Date of requesting appeal against examiner's decision of rejection]

[Date of extinction of right]

20.04.2000 26.02.2002

2006/11/10

THIS PAGE BLANK (USPTO)

٨

•

## JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely. 2.\*\*\*\* shows the word which can not be translated.

3.In the drawings, any words are not translated.

### CLAIMS

#### [Claim(s)]

[Claim 1] The semiconductor chip (12) carried in the substrate (11), and the connection terminal for power sources electrically connected with a power-source pad among the electrode pads (12a) formed in this semiconductor chip (12) (13 31), in the semiconductor device possessing two or more external connection terminals constituted with the connection terminal for glands (14 32) electrically connected with a grand pad, and the connection terminal for signals (15 33) electrically connected with a signal pad The semiconductor device characterized by arranging the arrangement side in which this connection terminal for power sources (13 31) and this connection terminal for glands (14.32) in this substrate (11) are arranged in the arrangement side in which this connection terminal for signals (15 33) in this substrate (11) is arranged, and a different field.

[Claim 2] The semiconductor device according to claim 1 characterized by arranging in the tooth back to the field where this connection terminal for power sources (13) and this connection terminal for glands (14) were carried in this semiconductor chip (12) of this substrate (11) while arranging in the field where this connection terminal for signals (15) was carried in this semiconductor chip (12) of this substrate (11).

[Claim 3] The semiconductor device according to claim 2 characterized by arranging so that this connection terminal for glands (14 32) may surround this connection terminal for power sources (13 31).

[Claim 4] The beer formed by penetrating this substrate (11) in this connection terminal for power sources (13), and this connection terminal for glands (14) (21, 22, 25, 26), The semiconductor device according to claim 2 or 3 characterized by constituting by the bump (23 27) electrically connected with this beer (22 26) in the tooth back to the field in which this semiconductor chip (12) of this substrate (11) was carried.

[Claim 5] The semiconductor device according to claim 1 characterized by arranging in the tooth back to the field where this connection terminal for signals (33) was carried in this semiconductor chip (12) of this substrate (11) while arranging in the field where this connection terminal for power sources (31) and this connection terminal for glands (32) were carried in this semiconductor chip (12) of this substrate (11) while arranging in the field where this connection terminal for power sources (31) and this connection terminal for glands (32) were carried in this semiconductor chip (12) of this substrate (11).

[Claim 6] The semiconductor device according to claim 5 characterized by constituting this connection terminal for signals (33) by the bump (39) electrically connected with this beer (38) in the tooth back to the beer (37 38) formed by penetrating this substrate (11), and the field in which this semiconductor chip (12) of this substrate (11) was carried.

[Translation done.]

\* NOTICES \*

JPO and NCIP! are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely. 2.\*\*\*\* shows the word which can not be translated. 3. In the drawings, any words are not translated.

### DETAILED DESCRIPTION

[Detailed Description of the Invention]

[0001]

[Industrial Application] This invention relates to the semiconductor device which is applied to a semiconductor device, especially has many external connection terminals.

[0002] In recent years, improvement in the speed and high integration of a semiconductor device are progressing, and **\*\*** pitch-ization of external connection terminals (a lead, pin, etc.) is called for by the miniaturization of the package accompanying this. Moreover, in addition to the above-mentioned miniaturization, the semiconductor device is expected improvement in an electrical property strongly. [0003]

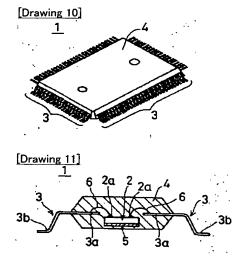

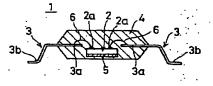

[Description of the Prior Art] Drawing A is an external view showing an example of the conventional semiconductor device 1, and drawing B is a sectional view of a semiconductor device 1. At the example shown in this drawing, it is QFP (Quad Flat Package). The semiconductor device 1 of the package structure of a type is shown.

[0004] As shown in each drawing, if the profile of the semiconductor device 1 is carried out, it is constituted by the semiconductor chip 2, the lead 3, and the resin package 4 grade. The semiconductor chip 2 is carried in the upper part of a stage 5, and electrode pad 2a and inner lead section 3a of lead 3 which were formed in the upper part of this semiconductor chip 2 are connected by the wire 6.

[0005] While a large number arrangement of the lead 3 is carried out so that a semiconductor chip 2 may be surrounded, and the inner lead section 3a is connected with a semiconductor chip 2 through a wire 6 as mentioned above, outer lead section 3b extends to the exterior of the resin package 4, and forms an external connection terminal. This outer lead section 3b is fabricated in the shape of a gull wing, in order to carry out the surface mount of the semiconductor device 1. Moreover, the resin package 4 is carrying out the resin seal of the above-mentioned semiconductor chip 2, inner lead section 3a, and the wire 6 grade to the interior, and these components are protected by the resin package 4.

[0006] As described above, the densification of a semiconductor chip 2 is progressing in recent years, and the number of electrode pad 2a formed in a semiconductor chip 2 is also increasing (200 or more pads). Moreover, since lead 3 is what is arranged corresponding to the number of electrode pad 2a, when the number of electrode pad 2a increases, it is in the inclination for the number of leads 3 to also increase.

[0007] On the other hand, electrode pad 2a is roughly classified into three kinds on electrical characteristics. They are three kinds of pads (it is called a grand pad) for performing the pad (it being called a power-source pad) for specifically supplying the pad (it being called the signal pad) and power source which deliver and receive a signal, and touch-down. Therefore, the classification with the same said of the lead 3 connected to electrode pad 2a can be performed (it is called a signal lead, a power lead, and a grand lead).

[0008] With the semiconductor device 1 of a configuration, it considered as the configuration which each lead 3 of this signal lead, a power lead, and a grand lead is turned [ configuration ] to the method of outside [ side face / of the resin package 4 / periphery 4 ], and makes it extend altogether irrespective of that class conventionally.

[0009]

[Problem(s) to be Solved by the Invention] However, with the semiconductor device of a configuration, each lead of a signal lead, a power lead, and a grand lead was conventionally considered as the configuration made to extend towards the method of outside [ side face / of a resin package / periphery 4 ] altogether irrespective of the class as mentioned above. For this reason, the part in which a signal lead adjoins a power lead and is arranged will arise inevitably.

[0010] Thus, in the part to which the signal lead adjoined the power lead, the noise of a power source will interfere in a signal lead, it becomes impossible for transfer of a signal to carry out proper, and the dependability of a semiconductor device will fall.

[0011] If the densification of a semiconductor chip progresses and the number of leads increases especially, since the magnitude of a resin package is not enlargeable from the miniaturization demand of a semiconductor device, each pitch between leads is formed into a **\*\*** pitch. For this reason, the effect of the power-source noise to the above-mentioned signal lead will pose a serious problem, if the number of leads increases.

[0012] Therefore, the area of a power lead and a grand lead wants for a power lead and a grand lead to have the desirable one where the electric resistance is smaller, and to enlarge [ one ] them if possible on the other hand. however, in a semiconductor device with many [ as mentioned above ] leads, while attaining **\*\*** pitch-ization of each pitch between leads, width of face of lead confidence is not narrowed, either — take — there is nothing. Therefore, area of a power lead and a grand lead could not be enlarged, but there was a trouble that the electrical characteristics of a power lead and a grand lead could not be enlarged.

[0013] This invention is made in view of the above-mentioned point, and it aims at offering the semiconductor device which can aim at improvement in the electrical property of a semiconductor device, and dependability.

### [0014]

[Means for Solving the Problem] The above-mentioned technical problem is solvable with \*\* 1 which provides each following means.

[0015] The semiconductor chip by which substrate loading was carried out in invention of claim 1, and the connection terminal for power sources electrically connected with a power-source pad among the electrode pads formed in this semiconductor chip. In the semiconductor device possessing two or more external connection terminals constituted with the connection terminal for glands electrically connected with a grand pad, and the connection terminal for signals electrically connected with a signal pad It is characterized by arranging the arrangement side in which the connection terminal for power sources and the connection terminal for glands in the above-mentioned substrate are arranged in the arrangement side in which the connection terminal for signals in the above-mentioned substrate is arranged, and a different field.

[0016] Moreover, in invention of claim 2, while arranging in the field where the above-mentioned connection terminal for signals was carried in the semiconductor chip of a substrate, it is characterized by arranging in the tooth back to the field where the above-mentioned connection terminal for power sources and the connection terminal for glands were carried in the semiconductor chip of a substrate.

[0017] Moreover, in invention of claim 3, it is characterized by arranging so that the above-mentioned connection terminal for glands may surround the connection terminal for power sources.

[0018] Moreover, it is characterized by constituting the above-mentioned connection terminal for glands, and the connection terminal for power sources from invention of claim 4 by the beer formed by penetrating a substrate, and the bump electrically connected with the above-mentioned beer in the tooth back to the field in which the semiconductor chip of a substrate was carried.

[0019] Moreover, in invention of claim 5, while arranging in the field where the above-mentioned connection terminal for power sources and the

connection terminal for glands were carried in the semiconductor chip of a substrate, it is characterized by arranging in the tooth back to the field where the above-mentioned connection terminal for signals was carried in the semiconductor chip of a substrate.

[0020] Furthermore, it is characterized by constituting the above-mentioned connection terminal for signals from invention of claim 6 by the beer formed by penetrating a substrate, and the bump electrically connected with the above-mentioned beer in the tooth back to the field in which the semiconductor chip of a substrate was carried.

#### [0021]

[Function] Each above-mentioned means acts as follows.

[0022] The arrangement side of the connection terminal [ in / according to invention of claim 1, the arrangement location of the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals is separated, and / a substrate ] for power sources, and the connection terminal for glands, By having arranged in a different field (location) the arrangement side in which the connection terminal for signals is arranged, it becomes possible to make the connection terminal for power sources and the connection terminal for signals estrange.

[0023] thus, the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals — alienation by being arranged, it can prevent that a noise mixes in the signal with which a power-source noise can reduce the effect affect the connection terminal for signals, and is delivered and received through the connection terminal for signals.

[0024] Moreover, since the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals are arranged in the field where substrates differ, it becomes possible to take a large arrangement area of the connection terminal for power sources, and the connection terminal for glands especially, and electric resistance of the connection terminal for power sources and the connection terminal for glands especially, and electric resistance of the connection terminal for power sources and the connection terminal for glands can be reduced. Therefore, the electrical property of a semiconductor device can be raised.

[0025] To moreover, the field as for which a substrate carries out [ the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals ] phase opposite according to invention of claim 2 or claim 5 (that is, if the field in which the semiconductor chip was carried is used as a top face) Since it becomes the configuration arranged in the top face and the tooth back by dissociating, the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals can be made to estrange greatly on a substrate. Therefore, a power-source noise can reduce effectively the effect affect the connection terminal for signals.

[0026] Moreover, according to invention of claim 3, since it becomes the configuration that the connection terminal for power sources was shielded with the connection terminal for glands, by being arranged so that the connection terminal for glands may surround the connection terminal for power sources, it can prevent that the power-source noise generated from the connection terminal for power sources has a bad influence on the exterior of the connection terminal for glands.

[0027] Moreover, according to invention of claim 4 or claim 6, the above-mentioned terminal can be pulled out to the tooth-back side of a substrate with an easy configuration by having constituted the connection terminal pulled out at the tooth-back side of a substrate by the beer formed by penetrating a substrate, and the bump electrically connected with this beer.

[0028]

[Example] Next, the example of this invention is explained with a drawing.

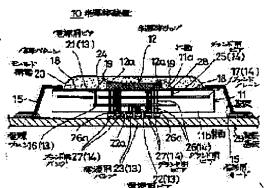

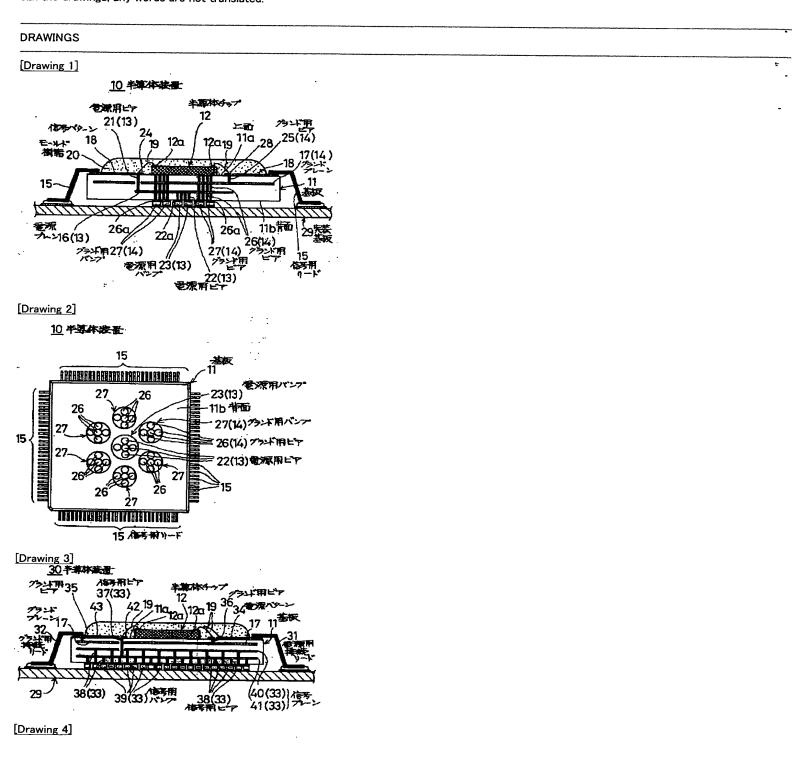

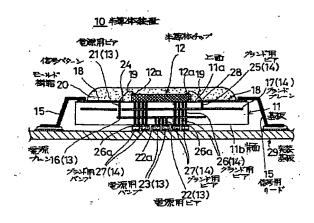

[0029] <u>Drawing 1</u> is the sectional view of the semiconductor device 10 which is the 1st example of this invention, and <u>drawing 2</u> is the bottom view of a semiconductor device 10.

[0030] If the profile of the semiconductor device 10 shown in each drawing is carried out, it is constituted by a substrate 11, the semiconductor chip 12, the connection terminal 13 for power sources, the connection terminal 14 for glands, and the lead 15 grade for signals.

[0031] A substrate 11 is a ceramic substrate by which multilayer formation was carried out, and the power plane 16 and the ground plane 17 are formed in the interior. This power plane 16 and ground plane 17 are the electrode layer formed with the conductive metal (for example, copper). Moreover, many signal patterns 18 are formed in top-face 11a of a substrate 11.

[0032] Moreover, the semiconductor chip 12 is being fixed to the upper part of a substrate 11, and electrode pad 12a is formed in the top face. Densification of this semiconductor chip 12 is carried out, and, therefore, much electrode pad 12a (200 or more [ for example, ]) is arranged.

[0033] This electrode pad 12a is classified into three kinds, a power-source pad, a grand pad, and a signal pad, on that property. A power-source pad is a pad for carrying out current supply to a semiconductor chip 12, a grand pad is a pad grounded and a signal pad is a pad with which a signal for a semiconductor chip 12 to perform predetermined processing is delivered and received further.

[0034] Two or more above-mentioned electrode pad 12a is connected to the connection terminal 13 for power sources which constitutes an external connection terminal, the connection terminal 14 for glands, and the lead 15 for signals. A power-source pad is connected with the connection terminal 13 for power sources, a grand pad is connected with the connection terminal 14 for glands, and, specifically, a signal pad is connected with the lead 15 for signals.

[0035] Moreover, electrical installation with each electrode pad 12a, the connection terminal 13 for power sources, the connection terminal 14 for glands, and the lead 15 for signals is performed using the wire 19. This wire 19 is arranged using wirebonding equipment between electrode pad 12a and each connection terminals 13, 14, and 15.

[0036] Furthermore, mold resin 20 is formed in the upper part of the semiconductor chip 12 arranged in the upper part of a substrate 11. In order to protect a semiconductor chip 12, a wire 19, and the signal pattern 18, this mold resin 20 is formed so that top-face 11a of a substrate 11 may be covered.

[0037] Then, the concrete configuration of the connection terminal 13 for power sources, the connection terminal 14 for glands, and the lead 15 for signals is explained.

[0038] The connection terminal 13 for power sources is constituted by the beer 21 and 22 for power sources, the bump 23 for power sources, and the above mentioned power-plane 16 grade. The beer 21 and 22 for power sources is considered as the configuration which filled up with copper powder the hole formed in the substrate 11, and gave conductivity to it. The beer 21 for power sources located in the upper part has connected the lower limit with the above mentioned power-plane 16 electrically while the upper limit is connected with the power-source pattern 24 formed in top-face 11a of a substrate 11.

[0039] Moreover, the lower limit is electrically connected by the beer 22 for power sources arranged by the lower part with the bump 23 for power sources by whom it was formed in tooth-back 11b of a substrate 11 while electrical installation of the upper limit was carried out to the power plane 16. This bump 23 for power sources is considered as the configuration which prepared for example, the solder ball in electrode 22a formed in the lower limit section of the beer 22 for power sources.

[0040] The above-mentioned power-source pattern 24 is connected with the semiconductor chip 12 by the wire 19, and the power-source pad currently therefore formed in the semiconductor chip 12 with the connection terminal 13 for power sources serves as a configuration pulled out by tooth-back 11b of a substrate 11. Moreover, although the arrangement location of the beer 21 for power sources located in the upper part will be arranged in the location corresponding to the location of the power-source pad formed in the semiconductor chip 12, the arrangement location of the beer 22 for power sources arranged by the lower part can be set as arbitration by forming a power plane 16. In this example, an arrangement location is selected by the abbreviation mid gear of a substrate 11, and the beer 22 for power sources is.

[0041] Moreover, the connection terminal 14 for glands is constituted by the beer 25 and 26 for glands, the bump 27 for glands, and the above mentioned ground plane 17 grade. The beer 25 and 26 for glands is considered as the configuration which filled up with copper powder the hole formed in the substrate 11 like the above mentioned beer 21 and 22 for power sources, and gave conductivity to it.

[0042] The upper limit section of the beer 25 for glands arranged in the upper part is connected with the grand pattern 28 formed in top-face 11a of a

substrate 11, and the lower limit is electrically connected with the ground plane 17. Moreover, the lower limit section is pulled out for the beer 26 for glands arranged by the lower part to tooth-back 11b of a substrate 11 while a predetermined location is electrically connected with a ground plane 17. The bump 27 for glands is arranged in this lower limit section. This bump 27 for glands is considered as the configuration which prepared the solder ball in electrode 26a formed in the lower limit section of the beer 26 for glands like the above mentioned bump 23 for power sources.

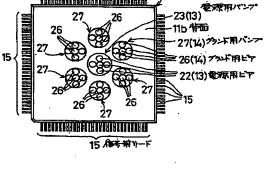

[0043] The above-mentioned grand pattern 28 is connected with the semiconductor chip 12 by the wire 19, and the grand pad currently therefore formed in the semiconductor chip 12 with the connection terminal 14 for glands serves as a configuration pulled out by tooth-back 11b of a substrate 11. Moreover, although the arrangement location of the beer 25 for glands located in the upper part will be arranged in the location corresponding to the location of the grand pad formed in the semiconductor chip 12, the arrangement location of the beer 26 for glands arranged by the lower part can be set as arbitration by forming a ground plane 17. In this example, as shown in <u>drawing 2</u>, an arrangement location is selected and the arrangement location of the beer 26 for glands is so that the beer 22 for power sources may be surrounded.

[0044] Moreover, the lead 15 for signals is formed with lead material, such as for example, 42alloy(s) (iron nickel alloy), and is arranged in the top face of a substrate 11. That is, the lead 15 for signals is considered as the configuration arranged in top-face 11a of the substrate 11 which is a different field from tooth-back 11b of the substrate 11 with which the above mentioned connection terminal 13 for power sources and the above mentioned connection terminal 14 for glands are pulled out. While this lead 15 for signals is electrically connected with the signal pattern 18 with which that inner lead part is formed in top-face 11a of a substrate 11, the outer lead part is considered as the configuration which extended to the method of outside [ substrate / 11 ]. Moreover, the outer lead part of the lead 15 for signals is fabricated in the shape of a gull wing, in order to consider a semiconductor device 10 as the configuration in which a surface mount is possible.

[0045] In addition, <u>drawing 1</u> shows the condition of having mounted the semiconductor device 10 in the mounting substrate 29. The pad for power sources, the pad for glands, and the pad for signals are formed in the top face of the mounting substrate 29, and the above mentioned connection terminal 13 for power sources, the connection terminal 14 for glands, and the lead 15 for signals are connected with each corresponding, predetermined pad.

[0046] Here, intermediary \*\*\*\*\* is carried out at the connection terminal 13 for power sources considered as the above-mentioned configuration, the connection terminal 14 for glands, and the arrangement structure of the lead 15 for signals.

[0047] As described above, the connection terminal 13 for power sources and the connection terminal 14 for glands are considered as the configuration which penetrated the substrate 11 through each beer 21, 22, 25, and 26, and was pulled out by tooth-back 11b. On the other hand, the lead 15 for signals is arranged in top-face 11a of the substrate 11 which are the tooth back where the connection terminal 13 for power sources and the connection terminal 14 for glands were pulled out, and the field which counters.

[0048] Therefore, in the semiconductor device 10 concerning this example, it has the composition that the connection terminal 13 for power sources and the lead 15 for signals were estranged and arranged in the substrate 11. It can prevent that a power-source noise mixes in the signal with which the power-source noise generated with the connection terminal 13 for power sources influences the lead 15 for signals, and flows the lead 15 for signals by this (superposition).

[0049] Moreover, in the semiconductor device 10 applied to this example as mentioned above, the connection terminal 13 for power sources is considered as the configuration surrounded by the connection terminal 14 for glands. Since the connection terminal 14 for glands is grounded, it has a shielding effect. Therefore, since it is the configuration that the connection terminal 13 for power sources was surrounded with the connection terminal 14 for glands which has a shielding effect, it can prevent that the power-source noise generated with the connection terminal 13 for power sources is not revealed outside from the arrangement location of the connection terminal 14 for glands, and a power-source noise mixes in the lead 15 for signals also by this (superposition).

[0050] Furthermore, only the lead 15 for signals will be arranged in top-face 11a of a substrate 11 by having separated and arranged the connection terminal 13 for power sources and the connection terminal 14 for glands, and the lead 15 for signals. Therefore, when the signal pattern 18 formed in top-face 11a of a substrate 11 and the arrangement tooth space of the lead 15 for signals become large and make large area of the signal pattern 18 and the lead 15 for signals, electric resistance can be reduced and the electrical property of a semiconductor device 10 can be raised. Moreover, when area of the signal pattern 18 and the lead 15 for signals is made to be the same as usual, it becomes possible to attain the miniaturization of a substrate 11, and the miniaturization of a semiconductor device 10 can be attained.

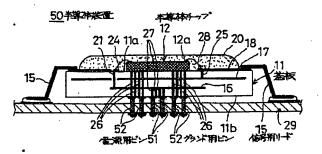

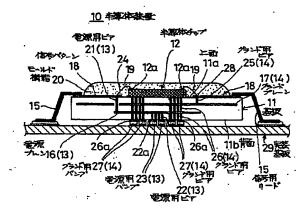

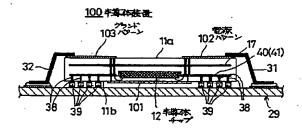

[0051] Then, the 2nd example of this invention is explained. <u>Drawing 3</u> shows the semiconductor device 30 which is the 2nd example of this invention. in addition, in each example which gives sequential explanation after the semiconductor device 30 concerning the 2nd example to be explained from now on, and explanation of the 2nd example, it is alike, it sets, the same sign is attached about the same component as the semiconductor device 10 concerning said 1st example carried out, and the explanation is omitted.

[0052] The semiconductor device 30 concerning the 2nd example is characterized by constituting so that the terminal 33 for signals may be pulled out by tooth-back 11b of a substrate 11 while it arranges the connection lead 31 for power sources, and the connection lead 32 for glands in top-face 11a of a substrate 11.

[0053] The connection lead 31 for power sources and the connection lead 32 for glands are formed with lead material, such as for example, 42alloy(s) (iron nickel alloy), and are arranged in the top face of a substrate 11. In order that that outer lead part may be considered as the configuration which extended towards the method of outside [ substrate / 11 ] and may make possible the surface mount of this connection lead 31 for power sources, and the connection lead 32 for glands, it is fabricated in the shape of a gull wing.

[0054] Moreover, it connects with the power-source pattern 34 currently formed in top-face 11a of a substrate 11 electrically, and the connection lead 31 for power sources is connected with the power-source pad of a semiconductor chip 12 through this power-source pattern 34 and a wire 19. [0055] Moreover, the connection lead 32 for glands is electrically connected with the ground plane 17 through the clan dopa turn 43 and the beer 35 for glands, and this ground plane 17 is connected with the grand pad through the beer 36 for KURANDO, and a wire 19.

[0056] On the other hand, the terminal 33 for signals is constituted by the beer 37 and 38 for signals, the bump 39 for signals and the signal plane 40, and 41 grades. The beer 37 and 38 for signals is considered as the configuration which filled up with copper powder the hole formed in the substrate 11, and gave conductivity to it.

[0057] The upper limit section of the beer 37 for signals arranged in the upper part is connected with the signal plattern 42 formed in top-face 11a of a substrate 11, and the lower limit is electrically connected with the signal plane 40 or the signal plane 41 (the condition of having connected with the signal plane 41 is shown by a diagram). Moreover, the lower limit section is pulled out for the beer 38 for signals arranged by the lower part to toothback 11b of a substrate 11 while the upper limit section is electrically connected with the signal plane 40 or the signal plane 41. The bump 39 for signals is arranged in this lower limit section. It considers as the configuration whose bump 39 for signals of this also prepared the solder ball in the electrode formed in the lower limit section of the beer 38 for signals.

[0058] The above-mentioned signal pattern 42 is connected with the semiconductor chip 12 by the wire 19, and the signal pad currently therefore formed in the semiconductor chip 12 with the terminal 33 for signals serves as a configuration pulled out by tooth-back 11b of a substrate 11. Moreover, although the arrangement location of the beer 37 for signals located in the upper part will be arranged in the location corresponding to the location of the signal pad formed in the semiconductor chip 12, the arrangement location of the beer 38 for signals arranged by the lower part can be set as arbitration by forming the signal planes 40 and 41. Therefore, it faces setting up the arrangement location of the beer 38 for signals with which transfer of various signals is performed, and this setting processing can be performed easily.

[0059] Since the connection lead 31 for power sources and the connection lead 32 for glands, and the terminal 33 for signals serve as the configuration which is pulled out by the field where substrates 11 differ and is arranged in it also in the semiconductor device 30 concerning the 2nd example considered as the above-mentioned configuration, it can prevent that a power-source noise mixes to the signal with which the power-source

noise which generates with the connection lead 31 for power sources influences the terminal 33 for signals, and flows the inside of the terminal 33 for signals (superposition).

[0060] Moreover, in the semiconductor device 30 concerning the 2nd example, it considers as the configuration in which the ground plane 17 was arranged between the power-source patterns 34 and the arrangement locations of the signal planes 40 and 41 which were formed in top-face 11a of a substrate 11. Since the ground plane 17 is grounded, it has a shielding effect. Therefore, since the power-source pattern 34 and the signal planes 40 and 41 are isolated electromagnetic by the ground plane 17 which has a shielding effect, it can prevent that the power-source noise generated by the power-source pattern 34 does not mix in the signal planes 40 and 41, and a power-source noise mixes in a signal also by this (superposition). [0061] Furthermore, by pulling out and arranging the connection lead 31 for power sources and the connection lead 32 for glands, and the terminal 33 for signals in the field where substrates 11 differ, a leeway is given in the arrangement location of the connection lead 31 for power sources, and the arrangement location of the electrical property of a semiconductor device 30 can be attained.

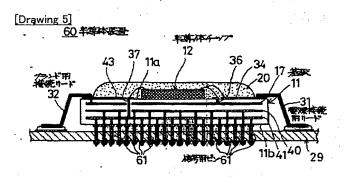

[0062] Drawing 4 shows the semiconductor device 50 which is the 3rd example of this invention.

[0063] The semiconductor device 10 concerning the 1st above mentioned example showed the example using the bump 23 for power sources, and the bump 27 for glands as a means for connecting electrically the connection terminal 13 for power sources, and the connection terminal 14 for glands with the pad formed in the mounting substrate 29.

[0064] On the other hand, in the semiconductor device 50 concerning the 3rd example, it is characterized by replacing with the bump 23 for power sources, and the bump 27 for glands, and considering as the configuration which formed the pin 51 for power sources, and the pin 52 for glands. Thus, especially the configuration that connects electrically the connection terminal 13 for power sources and the connection terminal 14 for glands with the pad formed in the mounting substrate 29 is not limited to face down structures, such as Bengbu, and can apply various structures. Moreover, effectiveness, such as mixing prevention of the power-source noise [ as opposed to a signal as the so-called PGA (Pin Grid Array) type structure ] using the pin 51 for power sources and the pin 52 for glands, improvement in an electrical property, and a miniaturization, can maintain a semiconductor device 50 like the 1st example and the 2nd example as mentioned above.

[0065] Drawing 5 shows the semiconductor device 50 which is the 4th example of this invention.

[0066] The semiconductor device 30 concerning the 2nd above mentioned example showed the example using the bump 39 for signals as a means for connecting the terminal 33 for signals with the pad formed in the mounting substrate 29 electrically. On the other hand, in the semiconductor device 60 concerning the 4th example, it is characterized by considering as the configuration which replaced with the bump 39 for signals and formed the pin 61 for signals. Mixing prevention of the power-source noise to a signal, the improvement in an electrical property, a miniaturization, etc. can be attained like the semiconductor devices 10, 30, and 50 applied to each above mentioned example also with the semiconductor device 60 concerning the 4th example considered as the above-mentioned configuration.

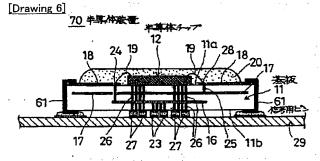

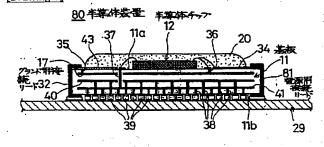

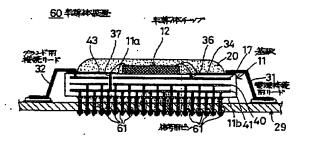

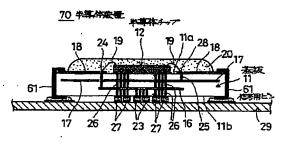

[0067] <u>Drawing 6</u> shows the semiconductor device 70 which is the 5th example of this invention, and <u>drawing 7</u> shows the semiconductor device 80 which is the 6th example of this invention.

[0068] In the semiconductor device 30 applied to the 2nd example in the semiconductor device 10 concerning the 1st above mentioned example, using the lead of a gull wing configuration as lead 15 for signals, the lead of a gull wing configuration was used as the connection lead 31 for power sources, and connection lead 32 for glands.

[0069] On the other hand, in the semiconductor device 70 concerning the 5th example, it is characterized by having replaced with the lead 15 for signals of a gull wing configuration, and establishing the so-called lead 71 for signals of J lead configuration. Moreover, in the semiconductor device 80 concerning the 6th example, it is characterized by having replaced with the connection lead 31 for power sources of a gull wing configuration, and the connection lead 32 for glands, and establishing the connection lead 81 for power sources of J lead configuration, and the connection lead 82 for glands.

[0070] Package structure of semiconductor devices 70 and 80 can be made into the package structure similar to QFJ (Quad Flat J-Leaded Package) structure by making each leads 71, 81, and 82 into J lead configuration as mentioned above. That is, in the semiconductor devices 70 and 80 concerning the 5th and 6th examples, it can consider as the configuration in which leads 71, 81, and 82 do not extend towards the method of outside [ substrate / 11 ]. Therefore, only the part to which leads 15, 31, and 32 had extended from the substrate 11 in the 1st thru/or the 4th example which described above the semiconductor devices 70 and 80 concerning the 5th and 6th examples can attain the miniaturization of semiconductor devices 70 and 80 concerning the 5th and 6th examples, the effectiveness of the 1st and 2nd above mentioned examples is maintainable.

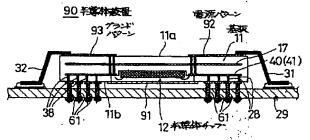

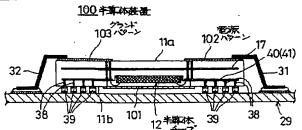

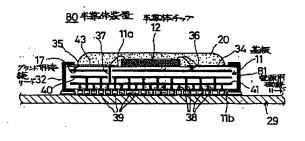

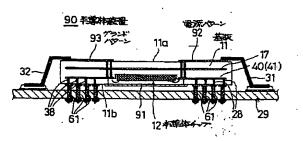

[0071] <u>Drawing 8</u> shows the semiconductor device 90 which is the 7th example of this invention, and <u>drawing 9</u> shows the semiconductor device 100 which is the 8th example of this invention.

[0072] The semiconductor device 90 concerning the 7th example is characterized by arranging a semiconductor chip 12 in tooth-back 11a of a substrate 11 in the semiconductor device 60 concerning the 4th above mentioned example, and is characterized by the semiconductor device 100 concerning the 8th example arranging a semiconductor chip 12 in tooth-back 11a of a substrate 11 in the semiconductor device 30 concerning the 2nd above mentioned example, and to close a semiconductor chip 12 to the exterior in each drawing.

[0073] In the semiconductor device 90,100 concerning the 7th example and the 8th example, since a large area is securable for top-face 11a of a substrate 11, by arranging the power-source pattern 92,102 and the grand pattern 93,103 in this top-face 11a, electric resistance of each pattern can be reduced greatly and the electrical property of a semiconductor device 90,100 can be raised further. In addition, of course also in the semiconductor device 90,100 concerning the 7th and 8th examples, the effectiveness of the 2nd and 3rd above mentioned examples is maintainable.

[Effect of the Invention] According to this invention, the following various effectiveness is done so like \*\*\*\*.

[0075] According to invention of claim 1, when it becomes possible to make the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals estrange, it can prevent that a noise mixes in the signal with which a power-source noise can reduce the effect affect the connection terminal for signals, and is delivered and received through the connection terminal for signals.

[0076] Moreover, it can become possible to take a large arrangement area of the connection terminal for power sources, and the connection terminal for glands, electric resistance of the connection terminal for power sources and the connection terminal for glands can be reduced, and, therefore, the electrical property of a semiconductor device can be raised.

[0077] Moreover, according to invention of claim 2 or claim 5, since the connection terminal for power sources and the connection terminal for glands, and the connection terminal for signals can be made to estrange greatly on a substrate, a power-source noise can reduce effectively the effect affect the connection terminal for signals.

[0078] Moreover, since the connection terminal for power sources serves as a configuration shielded with the connection terminal for glands according to invention of claim 3, it can prevent that the power-source noise generated from the connection terminal for power sources has a bad influence on the exterior of the connection terminal for glands.

[0079] Furthermore, according to invention of claim 4 or claim 6, each above-mentioned terminal can be pulled out to the tooth-back side of a substrate with an easy configuration by having constituted the connection terminal pulled out at the tooth-back side of a substrate by the beer formed by penetrating a substrate, and the bump electrically connected with this beer.

[Translation done.]

JP,08-008355,A [DESCRIPTION OF DRAWINGS]

\* NOTICES \*

### JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely. 2.\*\*\*\* shows the word which can not be translated. 3.In the drawings, any words are not translated.

#### DESCRIPTION OF DRAWINGS

### [Brief Description of the Drawings] [Drawing 1] It is the sectional view showing the semiconductor device which is the 1st example of this invention. [Drawing 2] It is the bottom view showing the semiconductor device which is the 1st example of this invention. [Drawing 3] It is the sectional view showing the semiconductor device which is the 2nd example of this invention. [Drawing 4] It is the sectional view showing the semiconductor device which is the 3rd example of this invention. [Drawing 5] It is the sectional view showing the semiconductor device which is the 4th example of this invention. [Drawing 6] It is the sectional view showing the semiconductor device which is the 5th example of this invention. [Drawing 7] It is the sectional view showing the semiconductor device which is the 6th example of this invention. [Drawing 8] It is the sectional view showing the semiconductor device which is the 7th example of this invention. [Drawing 9] It is the sectional view showing the semiconductor device which is the 8th example of this invention. [Drawing 10] It is the perspective view showing an example of the conventional semiconductor device. [Drawing 11] It is the sectional view showing an example of the conventional semiconductor device. [Description of Notations] 10, 30, 50, 60, 70, 80, 90 Semiconductor device 11 Substrate 11a Top face 11b Tooth back 12 Semiconductor Chip 13 Connection Terminal for Power Sources 14 Connection Terminal for Glands 15 71 Lead for signals 16 Power Plane 17 Plane for Glands 18 Signal Pattern 20 Mold Resin 31 22 Beer for power sources

23 Bump for Power Sources

24 92 102 Power-source pattern 25 26 Beer for glands

27 Bump for Glands

28 93,103 Grand pattern

29 Mounting Substrate ---

31 81 Connection lead for power sources

32 82 Connection lead for glands

33 Terminal for Signals

35 36 Beer for glands

37 38 Beer for signals

**39 Bump for Signals**

40 41 Signal play

42 Signal Pattern

51 Pin for Signals

52 Pin for Glands 61 Pin for Signals

[Translation done.]

### JP,08-008355,A [DRAWINGS]

\* NOTICES \*

# JPO and NCIPI are not responsible for any damages caused by the use of this translation.

This document has been translated by computer. So the translation may not reflect the original precisely.

\*\*\*\* shows the word which can not be translated.

In the drawings, any words are not translated.

[Drawing 7]

[Drawing 8]

### JP,08-008355,A [DRAWINGS]

[Translation done.]

(12) 公開特許公報(A)

## (11)特許出願公開番号

特開平8-8355

(43)公開日 平成8年(1996)1月12日

| (51) Int.Cl. <sup>6</sup> | 識別記号 | 庁内整理番号 | FI         | 技術表示箇所 |

|---------------------------|------|--------|------------|--------|

| H01L 23/12                |      |        | H01L 23/12 | E      |

審査請求 未請求 請求項の数6 OL (全 9 頁)

| <ul> <li>(22)出顧日 平成6年(1994)6月21日 神奈川県川崎市中原区上小田中101</li> <li>(72)発明者 山西 学雄<br/>神奈川県川崎市中原区上小田中101<br/>富士通株式会社内</li> <li>(72)発明者 辻村 剛久</li> </ul> | (21)出顧番号 | 特顧平6-138770     | (71) 出題人 000005223<br>富士通株式会社         |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|---------------------------------------|

| 富士通株式会社内<br>(72)発明者 辻村 剛久<br>神奈川県川崎市中原区上小田中10]<br>富士通株式会社内                                                                                     | (22)出顧日  | 平成6年(1994)6月21日 | 神奈川県川崎市中原区上小田中1015番地<br>(72)発明者 山西 学雄 |

| 神奈川県川崎市中原区上小田中101<br>富士通株式会社内                                                                                                                  |          | ·               |                                       |

| (74)代理人 弁理士 伊東 忠彦                                                                                                                              |          |                 | 神奈川県川崎市中原区上小田中1015番地                  |

|                                                                                                                                                |          | ·               | (74)代理人 弁理士 伊東 忠彦                     |

|                                                                                                                                                |          |                 |                                       |

(54)【発明の名称】 半導体装置

(57)【要約】

【目的】本発明は多数の外部接続端子を有する半導体装置に関し、半導体装置の電気特性及び信頼性の向上を図ることを目的とする。

【構成】基板11に搭載された半導体チップ12と、との半 導体チップ12に形成された電極バッド12aの内、電源バ ッドと電気的に接続される電源用接続端子13と、グラン ドパッドと電気的に接続されるグランド用接続端子14 と、信号バッドと電気的に接続される信号用リード15と により構成される複数の外部接続端子とを具備する半導 体装置において、上記基板11における電源用接続端子13 及びグランド用接続端子14が配設される配設面を、基板 11における信号用リード15が配設される配設面と異なる 面に配設する。

【特許請求の範囲】

【請求項1】 基板(11)に搭載された半導体チップ (12)と、

1

該半導体チップ(12)に形成された電極バッド(12 a)の内、電源バッドと電気的に接続される電源用接続 端子(13,31)と、グランドバッドと電気的に接続 されるグランド用接続端子(14,32)と、信号バッ ドと電気的に接続される信号用接続端子(15,33) とにより構成される複数の外部接続端子とを具備する半 導体装置において、

該基板(11)における該電源用接続端子(13,3 1)及び該グランド用接続端子(14,32)が配設さ れる配設面を、該基板(11)における該信号用接続端 子(15,33)が配設される配設面と異なる面に配設 したことを特徴とする半導体装置。

【請求項2】 該信号用接続端子(15)を該基板(1 1)の該半導体チップ(12)が搭載された面に配設す ると共に、

該電源用接続端子(13)及び該グランド用接続端子 (14)を該基板(11)の該半導体チップ(12)が 20 搭載された面に対する背面に配設したことを特徴とする 請求項1記載の半導体装置。

【請求項3】 該グランド用接続端子(14,32)が 該電源用接続端子(13,31)を囲繞するよう配設し たことを特徴とする請求項2記載の半導体装置。

【請求項4】 該電源用接続端子(13)及び該グラン ド用接続端子(14)を、該基板(11)を貫通して形 成されたビア(21,22,25,26)と、該基板 (11)の該半導体チップ(12)が搭載された面に対 する背面において該ビア(22,26)と電気的に接続 30 されたバンプ(23,27)とにより構成したことを特 徴とする請求項2または3記載の半導体装置。

【請求項5】 該電源用接続端子(31)及び該グラン ド用接続端子(32)を該基板(12)の該半導体チッ プ(12)が搭載された面に配設すると共に、

該信号用接続端子(33)を該基板(11)の該半導体 チップ(12)が搭載された面に対する背面に配設した ことを特徴とする請求項1記載の半導体装置。

【請求項6】 該信号用接続端子(33)を、該基板 (11)を貫通して形成されたビア(37,38)と、 該基板(11)の該半導体チップ(12)が搭載された 面に対する背面において該ビア(38)と電気的に接続 されたバンプ(39)とにより構成したことを特徴とす る請求項5記載の半導体装置。

【発明の詳細な説明】

[0001]

【産業上の利用分野】本発明は半導体装置に係り、特に 多数の外部接続端子を有する半導体装置に関する。 【0002】近年、半導体装置の高速化及び高集積化が

進んでおり、これに伴うパッケージの小型化により、外 50

部接続端子(リード,ピン等)の狭ピッチ化が求められ ている。また、上記の小型化に加えて半導体装置には電 気特性の向上が強く望まれている。

2

[0003]

【従来の技術】図Aは従来の半導体装置1の一例を示す 外観図であり、また図Bは半導体装置1の断面図であ る。同図に示す例では、QFP(Quad Flat Package)タ イプのバッケージ構造の半導体装置1を示している。

【0004】各図に示されるように、半導体装置1は大 10 略すると半導体チップ2, リード3, 樹脂パッケージ4

等により構成されている。半導体チップ2はステージ5 の上部に搭載されており、この半導体チップ2の上部に 形成された電極パッド2aとリード3のインナーリード 部3aとはワイヤ6により接続されている。

【0005】リード3は、半導体チップ2を囲繞するよ う多数配設されており、そのインナーリード部3aは上 記のようにワイヤ6を介して半導体チップ2と接続され ると共に、アウターリード部3bは樹脂パッケージ4の 外部に延出し外部接続端子を形成する。このアウターリ

ード部3bは、半導体装置1を表面実装するためにガル ウイング状に成形されている。また、樹脂バッケージ4 はその内部に上記の半導体チップ2、インナーリード部 3a、ワイヤ6等を樹脂封止しており、これらの構成要 素は樹脂パッケージ4により保護されている。

【0006】前記したように、近年半導体チップ2の高 密度化が進んでおり、半導体チップ2に形成される電極 パッド2 aの数も増大している(200パッド以上)。 また、リード3は電極パッド2 aの数に対応して配設さ れるものであるため、電極パッド2 aの数が増大するこ とによりリード3の数も増大する傾向にある。

[0007]一方、電極パッド2aは電気的特性上、3 種類に大きく分類される。具体的には、信号の授受を行 うパッド(信号パッドという)、電源を供給するための パッド(電源パッドという)、接地を行うためのパッド (グランドパッドという)の三種類である。よって、電 極パッド2aに接続されるリード3も同様の分類を行う ことができる(信号リード,電源リード,グランドリー ドという)。

【0008】従来構成の半導体装置1では、この信号リ 40 ード、電源リード、グランドリードの各リード3を、そ の種類に拘わらず全て樹脂パッケージ4の外周四側面よ り外方に向けて延出させる構成とされていた。

[0009]

【発明が解決しようとする課題】しかるに従来構成の半 導体装置では、上記のように信号リード,電源リード, グランドリードの各リードがその種類に拘わらず全て樹 脂パッケージの外周四側面より外方に向けて延出させる 構成とされていた。このため、信号リードが電源リード と隣接して配設される部分が必然的に生じてしまう。 【0010】このように、信号リードが電源リードと隣 3

接した部位においては電源のノイズが信号リードに干渉 し、信号の授受が適正に行うことができなくなり、半導 体装置の信頼性が低下してしまう。

【0011】特に、半導体チップの高密度化が進みリー ド数が増大すると、樹脂パッケージの大きさは半導体装 置の小型化要求より大型化することはできないため、各 リード間ピッチは狭ピッチ化する。このため、上記の信 号リードに対する電源ノイズの影響は、リード数が増大 すると重大な問題となる。

【0012】一方、電源リード及びグランドリードはそ 10 の電気的抵抗が小さいほうが望ましく、よって電源リー ド及びグランドリードの面積はなるべく大きくしたい。 しかるに、上記のようにリード数の多い半導体装置で は、各リード間ピッチの狭ピッチ化を図ると共にリード 自信の幅も狭くせざるおえない。よって、電源リード及 びグランドリードの面積を大きくすることはできず、電 源リード及びグランドリードの電気的特性を向上させる ことはできないという問題点があった。

【0013】本発明は上記の点に鑑みてなされたもので あり、半導体装置の電気特性及び信頼性の向上を図るこ とができる半導体装置を提供することを目的とする。 [0014]

【課題を解決するための手段】上記課題は下記の各手段 を講じるこひとにより解決することができる。

【0015】請求項1の発明では、基板搭載された半導 体チップと、この半導体チップに形成された電極パッド の内、電源パッドと電気的に接続される電源用接続端子 と、グランドパッドと電気的に接続されるグランド用接 続端子と、信号バッドと電気的に接続される信号用接続 端子とにより構成される複数の外部接続端子とを具備す る半導体装置において、上記基板における電源用接続端 子及びグランド用接続端子が配設される配設面を、上記 基板における信号用接続端子が配設される配設面と異な る面に配設したことを特徴とするものである。

【0016】また、請求項2の発明では、上記信号用接 続端子を基板の半導体チップが搭載された面に配設する と共に、上記電源用接続端子及びグランド用接続端子を 基板の半導体チップが搭載された面に対する背面に配設 したことを特徴とするものである。

【0017】また、請求項3の発明では、上記グランド 用接続端子が電源用接続端子を囲繞するよう配設したこ とを特徴とするものである。

【0018】また、請求項4の発明では、上記グランド 用接続端子及び電源用接続端子を、基板を貫通して形成 されたビアと、基板の半導体チップが搭載された面に対 する背面において上記ビアと電気的に接続されたバンプ とにより構成したことを特徴とするものである。

【0019】また、請求項5の発明では、上記電源用接 続端子及びグランド用接続端子を基板の半導体チップが 搭載された面に配設すると共に、上記信号用接続端子を 50 【実施例】次に本発明の実施例について図面と共に説明

Δ

基板の半導体チップが搭載された面に対する背面に配設 したことを特徴とするものである。

【0020】更に、請求項6の発明では、上記信号用接 続端子を、基板を貫通して形成されたビアと、基板の半 導体チップが搭載された面に対する背面において上記ビ アと電気的に接続されたバンプとにより構成したことを 特徴とするものである。

[0021]

【作用】上記した各手段は、下記のように作用する。

【0022】請求項1の発明によれば、電源用接続端子 及びグランド用接続端子と信号用接続端子の配設位置を 分離し、基板における電源用接続端子及びグランド用接 続端子の配設面と、信号用接続端子が配設される配設面 とを異なる面(位置)に配設したことにより、電源用接 統端子及びグランド用接続端子と信号用接続端子とを離 間させることが可能となる。

【0023】 このように電源用接続端子及びグランド用 接続端子と信号用接続端子とが離間配設されることによ り、電源ノイズが信号用接続端子に及ぼす影響を低減す 20 ることができ、信号用接続端子を介して授受される信号 にノイズが混入することを防止することができる。

【0024】また、電源用接続端子及びグランド用接続 端子と信号用接続端子とが基板の異なる面に配設される ため、特に電源用接続端子及びグランド用接続端子の配 設面積を大きく取ることが可能となり、電源用接続端子 及びグランド用接続端子の電気的抵抗を低減することが できる。よって、半導体装置の電気特性を向上させると とができる。

【0025】また、請求項2或いは請求項5の発明によ 30 れば、電源用接続端子及びグランド用接続端子と信号用 接続端子とが、基板の相対向する面に(即ち半導体チッ ブが搭載された面を上面とすると、上面と背面に)分離 して配設された構成となるため、基板上において電源用 接続端子及びグランド用接続端子と信号用接続端子とを 大きく離間させることができる。よって、電源ノイズが 信号用接続端子に及ぼす影響を効果的に低減することが できる。

【0026】また、請求項3の発明によれば、グランド 用接続端子が電源用接続端子を囲繞するよう配設される 40 ことにより、電源用接続端子はグランド用接続端子によ

りシールドされた構成となるため、電源用接続端子から 発生する電源ノイズがグランド用接続端子の外部に悪影 響を及ぼすことを防止することができる。

【0027】また、請求項4或いは請求項6の発明によ れば、基板の背面側に引き出される接続端子を、基板を 貫通して形成されたビアと、このビアと電気的に接続さ れたバンプとにより構成したことにより、簡単な構成で 上記端子を基板の背面側に引き出すことができる。 [0028]

【0029】図1は本発明の第1実施例である半導体装置10の断面図であり、図2は半導体装置10の底面図である。

5

【0030】各図に示される半導体装置10は、大略す ると基板11,半導体チップ12,電源用接続端子1 3,グランド用接続端子14,及び信号用リード15等 により構成されている。

【0031】基板11は多層形成されたセラミック基板 であり、その内部には電源プレーン16及びグランドプ 10 レーン17が形成されている。この電源プレーン16及 びグランドプレーン17は導電性金属(例えば銅)によ り形成された電極層である。また、基板11の上面11 aには多数の信号パターン18が形成されている。

【0032】また、基板11の上部には半導体チップ1 2が固定されており、その上面には電極バッド12aが 形成されている。この半導体チップ12は高密度化され たものであり、よって多数の電極バッド12a(例え ば、200以上)が配設されている。

[0033] この電極パッド12aは、その性質上、電 20 源パッド、グランドパッド、信号パッドの3種類に分類 される。電源パッドは半導体チップ12に対して電源供 給するためのパッドであり、グランドパッドは接地され るパッドであり、更に信号パッドは半導体チップ12が 所定の処理を行うための信号が授受されるパッドであ る。

【0034】上記の複数の電極パッド12aは、外部接 続端子を構成する電源用接続端子13,グランド用接続 端子14,及び信号用リード15に接続される。具体的 には、電源パッドは電源用接続端子13と接続され、グ ランドパッドはグランド用接続端子14と接続され、信 号パッドは信号用リード15と接続される。

【0035】また、各電極パッド12aと電源用接続端 子13, グランド用接続端子14,及び信号用リード1 5との電気的接続はワイヤ19を用いて行われている。 このワイヤ19は、ワイヤボンディング装置を用いて電 極パッド12aと各接続端子13,14,15との間に 配設される。

【0036】更に、基板11の上部に配設された半導体 チップ12の上部には、モールド樹脂20が形成されて いる。このモールド樹脂20は、半導体チップ12,ワ イヤ19,及び信号パターン18を保護するために、基 板11の上面11aを覆うように形成されている。

【0037】続いて、電源用接続端子13, グランド用 接続端子14, 及び信号用リード15の具体的構成につ いて説明する。

【0038】電源用接続端子13は、電源用ビア21,

に記設されるグランド用ビア26の配設位置は低

22、電源用バンプ23、及び前記した電源プレーン1

6等により構成されている。電源用ビア21,22は基

たるようにグランド用ビア26の配設位置は電源

板11に形成された孔に例えば銅粉を充填して導電性を 50 22を取り囲むように配設位置が選定されいる。

6

持たせた構成とされている。上部に位置する電源用ビア 21は、その上端が基板11の上面11aに形成された 電源パターン24と接続されると共に、その下端は前記 した電源プレーン16と電気的に接続している。 【0039】また、下部に配設された電源用ビア22は

上端が電源プレーン16と電気的接続されると共に、下 端は基板11の背面11bに形成された電源用バンプ2 3と電気的に接続されている。この電源用バンプ23 は、例えば半田ボールを電源用ビア22の下端部に形成 された電極22aに設けた構成とされている。

[0040]上記の電源バターン24はワイヤ19によ り半導体チップ12と接続されており、よって電源用接 続端子13により半導体チップ12に形成されている電 源バッドは基板11の背面11bに引き出された構成と なる。また、上部に位置する電源用ビア21の配設位置 は、半導体チップ12に形成された電源バッドの位置に 対応した位置に配設されることとなるが、電源フレーン 16を設けることにより下部に配設される電源用ビア2 2の配設位置は任意に設定することができる。本実施例 においては、電源用ビア22は基板11の略中央位置に 配設位置が選定されいる。

[0041]また、グランド用接続端子14は、グラン ド用ビア25,26、グランド用バンプ27、及び前記 したグランドプレーン17等により構成されている。グ ランド用ビア25,26は、前記した電源用ビア21, 22と同様に基板11に形成された孔に例えば銅粉を充 填して導電性を持たせた構成とされている。

【0042】上部に配設されるグランド用ビア25の上端部は、基板11の上面11aに形成されたグランドバターン28と接続されており、またその下端はグランドブレーン17と電気的に接続されている。また、下部に配設されるグランド用ビア26は、所定位置がグランドプレーン17と電気的に接続されると共に、下端部は基板11の背面11bまで引き出されている。との下端部にはグランド用バンプ27が配設されている。とのグランド用バンプ27は、前記した電源用バンプ23と同様に、例えば半田ボールをグランド用ビア26の下端部に形成された電極26aに設けた構成とされている。

【0043】上記のグランドパターン28はワイヤ19

40 により半導体チップ12と接続されており、よってグランド用接続端子14により半導体チップ12に形成されているグランドバッドは基板11の背面11bに引き出された構成となる。また、上部に位置するグランド用ビア25の配設位置は、半導体チップ12に形成されたグランドバッドの位置に対応した位置に配設されることとなるが、グランドプレーン17を設けることにより下部に配設されるグランド用ビア26の配設位置は任意に設定することができる。本実施例においては、図2に示されるようにグランド用ビア26の配設位置は電源用ビア

50 22を取り囲れたらに可設位置が漂完されいる

する。

30

7

[0044]また、信号用リード15は例えば42alloy (鉄-ニッケル合金)等のリード材料により形成されて おり基板11の上面に配設されている。即ち、信号用リ ード15は、前記した電源用接続端子13及びグランド 用接続端子14が引き出される基板11の背面11bと 異なる面である基板11の上面11aに配設された構成 とされている。この信号用リード15は、そのインナー リード部分が基板11の上面11aに形成されている信 号パターン18と電気的に接続されると共に、アウター リード部分は基板11より外方に延出した構成とされて 10 いる。また、信号用リード15のアウターリード部分 は、半導体装置10を表面実装可能な構成とするために ガルウイング状に成形されている。

【0045】尚、図1は半導体装置10を実装基板29 に実装した状態を示している。実装基板29の上面に は、電源用バッド、グランド用バッド、信号用バッドが 形成されており、前記した電源用接続端子13、グラン ド用接続端子14、及び信号用リード15は、対応する 所定の各バッドと接続される。

【0046】CCで、上記構成とされた電源用接続端子 20 13, グランド用接続端子14,及び信号用リード15 の配設構造につてい考察する。

【0047】上記したように、電源用接続端子13及び グランド用接続端子14は、各ビア21,22,25, 26を介して基板11を貫通して背面11bに引き出さ れた構成とされている。これに対して、信号用リード1 5は電源用接続端子13及びグランド用接続端子14が 引き出された背面と対向する面である基板11の上面1 1aに配設されている。

【0048】従って、本実施例に係る半導体装置10で は、基板11内において電源用接続端子13と信号用リ ード15とが離間して配設された構成となっている。こ れにより、電源用接続端子13で発生する電源ノイズが 信号用リード15に影響し、信号用リード15を流れる 信号に電源ノイズが混入(重畳)するのを防止すること ができる。

【0049】また、上記のように本実施例に係る半導体 装置10では、電源用接続端子13はグランド用接続端 子14に囲繞された構成とされている。グランド用接続 端子14は接地されているためシールド効果を有する。 従って、シールド効果を有するグランド用接続端子14 により電源用接続端子13は取り囲まれた構成であるた め、電源用接続端子13で発生する電源ノイズがグラン ド用接続端子14の配設位置より外部に漏洩することは なく、これによっても信号用リード15に電源ノイズが 混入(重畳)するのを防止することができる。

【0050】更に、電源用接続端子13及びグランド用 では、信号プレーン41と接続された状態が示されてい 接続端子14と、信号用リード15とを分離して配設し る)。また、下部に配設される信号用ビア38は、上端 たことにより、基板11の上面11aには信号用リード 部が信号プレーン40或いは信号プレーン41と電気的 15のみが配設されることとなる。従って、基板110 50 に接続されると共に、下端部は基板11の背面11bま

8

上面11aに形成される信号パターン18及び信号用リ ード15の配設スペースが広くなり、信号パターン18 及び信号用リード15の面積を広くした場合には、電気 抵抗を低減することができ、半導体装置10の電気特性 を向上させることができる。また、信号パターン18及 び信号用リード15の面積を従来と同様とした場合に は、基板11の小型化を図ることが可能となり、半導体 装置10の小型化を図ることができる。

[0051] 続いて、本発明の第2実施例について説明 する。図3は本発明の第2実施例である半導体装置30 を示している。尚、これから説明する第2実施例に係る 半導体装置30、及び第2実施例の説明後に順次説明す る各実施例ににおいて、前記した第1実施例に係る半導 体装置10と同一構成部分については同一符号を付して その説明を省略する。

[0052]第2実施例に係る半導体装置30は、基板 11の上面11aに電源用接続リード31及びグランド 用接続リード32を配設すると共に、信号用端子33が 基板11の背面11bに引き出されるよう構成したこと を特徴とするものである。

[0053] 電源用接続リード31及びグランド用接続 リード32は例えば42alloy(鉄-ニッケル合金)等のリ ード材料により形成されており基板11の上面に配設さ れている。この電源用接続リード31及びグランド用接 続リード32は、そのアウターリード部分が基板11よ り外方に向け延出した構成とされており、表面実装可能 とするためにガルウイング状に成形されている。

【0054】また、電源用接続リード31は、基板11 の上面11aに形成されている電源パターン34と電気 的に接続されており、この電源パターン34,ワイヤ1 9を介して半導体チップ12の電源パッドと接続されて

いる。 【0055】また、グランド用接続リード32は、クラ ンドパターン43、グランド用ビア35を介してグラン ドプレーン17と電気的に接続されており、このグラン ドプレーン17はクランド用ビア36、ワイヤ19を介 してグランドパッドと接続されている。

【0056】一方、信号用端子33は信号用ビア37, 38、信号用バンブ39、及び信号ブレーン40,41

40 等により構成されている。信号用ビア37,38は、基 板11に形成された孔に例えば銅粉を充填して導電性を 持たせた構成とされている。

[0057]上部に配設される信号用ビア37の上端部 は、基板11の上面11aに形成された信号パターン4 2と接続されており、またその下端は信号ブレーン40 或いは信号ブレーン41と電気的に接続されている(図 では、信号ブレーン41と接続された状態が示されてい る)。また、下部に配設される信号用ビア38は、上端 部が信号ブレーン40或いは信号ブレーン41と電気的

る。

20

で引き出されている。この下端部には信号用バンプ39 が配設されている。との信号用バンプ39も例えば半田 ボールを信号用ビア38の下端部に形成された電極に設 けた構成とされている。

【0058】上記の信号パターン42はワイヤ19によ り半導体チップ12と接続されており、よって信号用端 子33により半導体チップ12に形成されている信号パ ッドは基板11の背面11bに引き出された構成とな る。また、上部に位置する信号用ビア37の配設位置 は、半導体チップ12に形成された信号パッドの位置に 10 対応した位置に配設されることとなるが、信号プレーン 40,41を設けることにより下部に配設される信号用 ビア38の配設位置は任意に設定することができる。よ って、種々の信号の授受が行われる信号用ビア38の配 設位置を設定するに際し、この設定処理を容易に行うこ とができる。

【0059】上記構成とされた第2実施例に係る半導体 装置30においても、電源用接続リード31及びグラン ド用接続リード32と信号用端子33とが基板11の異 なる面に引き出されて配設される構成となるため、電源 用接続リード31で発生する電源ノイズが信号用端子3 3に影響し、信号用端子33内を流れる信号に電源ノイ ズが混入(重畳)するのを防止することができる。

【0060】また、第2実施例に係る半導体装置30で は、基板11の上面11aに形成された電源パターン3 4と信号ブレーン40,41の配設位置との間にグラン ドプレーン17が配設された構成とされている。グラン ドプレーン17は接地されているためシールド効果を有 する。従って、シールド効果を有するグランドプレーン 17により電源パターン34と信号ブレーン40,41 とは電磁的に隔離されるため、電源パターン34で発生

する電源ノイズが信号ブレーン40,41に混入すると とはなく、これによっても電源ノイズが信号内に混入 (重畳)するのを防止することができる。

【0061】更に、電源用接続リード31及びグランド 用接続リード32と信号用端子33とが基板11の異な る面に引き出されて配設されることにより、第1実施例 と同様に電源用接続リード31及びグランド用接続リー ド32の配設位置、信号用端子33の配設位置に余裕が でき、これに起因して半導体装置30の電気特性の向上 40 及び小型化を図ることができる。

【0062】図4は本発明の第3実施例である半導体装 置50を示している。

【0063】前記した第1実施例に係る半導体装置10 では、電源用接続端子13及びグランド用接続端子14 を実装基板29に形成されたパッドと電気的に接続する ための手段として電源用バンプ23及びグランド用バン ブ27を用いた例を示した。

【0064】これに対し、第3実施例に係る半導体装置

10

に代えて、電源用ピン51及びグランド用ピン52を設 けた構成とすることを特徴とするものである。このよう に、電源用接続端子13及びグランド用接続端子14を 実装基板29に形成されたパッドと電気的に接続する構 成は特にパンプ等のフェイスダウン構造に限定されるも のではなく、種々の構造を適用することができる。ま た、上記のように半導体装置50を電源用ビン51及び グランド用ピン52を用いた、いわゆるPGA(Pin Gri d Array)タイプ構造としても、信号に対する電源ノイズ の混入防止、電気特性の向上、及び小型化等の効果は第 1実施例及び第2実施例と同様に維持することができ

【0065】図5は本発明の第4実施例である半導体装 置50を示している。

【0066】前記した第2実施例に係る半導体装置30 では、信号用端子33を実装基板29に形成されたパッ ドと電気的に接続するための手段として信号用バンプ3 9を用いた例を示した。これに対し、第4実施例に係る 半導体装置60では、信号用バンプ39に代えて信号用

ビン61を設けた構成とすることを特徴とするものであ る。上記構成とされた第4実施例に係る半導体装置60 でも、前記した各実施例に係る半導体装置10.30. 50と同様に信号に対する電源ノイズの混入防止、電気 特性の向上、及び小型化等を図ることができる。 【0067】図6は本発明の第5実施例である半導体装

置70を示しており、また図7は本発明の第6実施例で ある半導体装置80を示している。

【0068】前記した第1実施例に係る半導体装置10 では信号用リード15としてガルウイング形状のリード

を用い、また第2実施例に係る半導体装置30では電源 30 用接続リード31及びグランド用接続リード32として ガルウイング形状のリードを用いた。

【0069】これに対し、第5実施例に係る半導体装置 70では、ガルウイング形状の信号用リード15に代え て、いわゆるJリード形状の信号用リード71を設けた ことを特徴とするものである。また、第6実施例に係る 半導体装置80では、ガルウイング形状の電源用接続リ ード31及びグランド用接続リード32に代えて、Jリ ード形状の電源用接続リード81及びグランド用接続リ ード82を設けたことを特徴とするものである。

【0070】上記のように各リード71,81,82を Jリード形状とすることにより、半導体装置70,80 のパッケージ構造はQFJ (Quad Flat J-Leaded Packag e)構造と似たパッケージ構造とすることができる。即 ち、第5及び第6実施例に係る半導体装置70,80で は、リード71,81,82が基板11より外方に向け 延出しない構成とすることができる。よって、第5及び 第6実施例に係る半導体装置70,80は、前記した第 1乃至第4実施例においてリード15,31,32が基 50では、電源用バンプ23及びグランド用バンプ27 50 板11から延出していた分だけ半導体装置70,80の

11

小型化を図ることができる。尚、第5及び第6実施例に 係る半導体装置70,80においても、前記した第1及 び第2実施例の効果を維持できることは勿論である。

【0071】図8は本発明の第7実施例である半導体装 置90を示しており、また図9は本発明の第8実施例で ある半導体装置100を示している。

【0072】第7実施例に係る半導体装置90は、前記 した第4実施例に係る半導体装置60において半導体チ ップ12を基板11の背面11aに配設したことを特徴 は前記した第2実施例に係る半導体装置30において半 導体チップ12を基板11の背面11aに配設したこと を特徴とするものである。尚、各図において91,10 1はキャップであり、半導体チップ12を外部に対して 封止するために設けられている。

【0073】第7実施例及び第8実施例に係る半導体装 置90,100では、基板11の上面11aに広い面積 を確保することができるため、この上面11aに電源パ ターン92,102及びグランドパターン93,103 を配設することにより、各パターンの電気的抵抗を大き 20 く低減することができ、更に半導体装置90,100の 電気特性を向上させることができる。尚、第7及び第8 実施例に係る半導体装置90,100においても、前記 した第2及び第3実施例の効果を維持できることは勿論 である。

[0074]

【発明の効果】上述の如く本発明によれば、下記の種々 の効果を奏する。

【0075】請求項1の発明によれば、電源用接続端子 及びグランド用接続端子と信号用接続端子とを離間させ 30 ることが可能となることにより、電源ノイズが信号用接 続端子に及ぼす影響を低減することができ、信号用接続 端子を介して授受される信号にノイズが混入することを 防止することができる。

【0076】また、電源用接続端子及びグランド用接続 端子の配設面積を大きく取ることが可能となり、電源用 接続端子及びグランド用接続端子の電気的抵抗を低減す ることができ、よって半導体装置の電気特性を向上させ ることができる。

【0077】また、請求項2或いは請求項5の発明によ 40 れば、基板上において電源用接続端子及びグランド用接 続端子と信号用接続端子とを大きく離間させることがで きるため、電源ノイズが信号用接続端子に及ぼす影響を 効果的に低減することができる。

【0078】また、請求項3の発明によれば、電源用接 統端子はグランド用接続端子によりシールドされた構成 となるため、電源用接続端子から発生する電源ノイズが グランド用接続端子の外部に悪影響を及ぼすことを防止 することができる。

【0079】更に、請求項4或いは請求項6の発明によ 50 32,82 グランド用接続リード

12 **´れば、基板の背面側に引き出される接続端子を、基板を** 貫通して形成されたビアと、このビアと電気的に接続さ れたバンプとにより構成したことにより、簡単な構成で 上記各端子を基板の背面側に引き出すことができる。 【図面の簡単な説明】 【図1】本発明の第1実施例である半導体装置を示す断 面図である。 【図2】本発明の第1実施例である半導体装置を示す底 面図である。 とするものであり、第8実施例に係る半導体装置100 10 【図3】本発明の第2実施例である半導体装置を示す断 面図である。 【図4】本発明の第3実施例である半導体装置を示す断 面図である。 【図5】本発明の第4実施例である半導体装置を示す断 面図である。 【図6】本発明の第5実施例である半導体装置を示す断 面図である。 【図7】本発明の第6実施例である半導体装置を示す断 面図である。 【図8】本発明の第7実施例である半導体装置を示す断 面図である。 【図9】本発明の第8実施例である半導体装置を示す断 面図である。 【図10】従来の半導体装置の一例を示す斜視図であ る。 【図11】従来の半導体装置の一例を示す断面図であ る。 【符号の説明】 10,30,50,60,70,80,90 半導体装 圕 11 基板 11a 上面 11b 背面 12 半導体チップ 13 電源用接続端子 14 グランド用接続端子 15,71 信号用リード 16 電源プレーン 17 グランド用プレーン 18 信号パターン 20 モールド樹脂 31,22 電源用ビア 23 電源用バンプ 24,92,102 電源パターン 25,26 グランド用ビア 27 グランド用バンプ 28,93,103 グランドパターン 29 実装基板

- 31,81 電源用接続リード

33 信号用端子 35,36 グランド用ビア 37,38 信号用ビア 39 信号用バンプ

40,41 信号プレー

(8)

\*

14

\*42 信号パターン 51 信号用ビン 52 グランド用ピン

61 信号用ビン

<u>10</u>半算体发表

15

REMARKAN A CORRECT OF A DESCRIPTION OF A DESCRIPTA DESCRIPTA DESCRIPTION OF A DESCRIPTION OF A DESCRIPTION O

【図2】

【図4】

【図5】

【図6】

26 1ib

29

15 2

【図7】

【図8】

【図10】

0

【図11】

# THIS PAGE BLANK autor